Die steigende Nachfrage nach künstlicher Intelligenz belastet die globale Rechenkapazität und zwingt Halbleiterhersteller dazu, der Energieeffizienz mehr denn je Priorität einzuräumen. Vor diesem Hintergrund ist PowerLattice, ein 2023 von Veteranen von Qualcomm, NUVIA und Intel gegründetes Startup, mit einer möglicherweise bahnbrechenden Lösung hervorgegangen: einem Chiplet, das den Stromverbrauch um über 50 % reduzieren soll. Am Montag kündigte das Unternehmen eine Serie-A-Finanzierungsrunde in Höhe von 25 Millionen US-Dollar an, angeführt von Playground Global und Celesta Capital, wodurch sich die Gesamtfinanzierung auf 31 Millionen US-Dollar erhöht.

Das Problem: KIs Machthunger

Große Sprachmodelle und andere KI-Anwendungen erfordern riesige Rechenzentren für Training und Inferenz, was den Energiebedarf exponentiell in die Höhe treibt. Bei der Reduzierung des Stromverbrauchs geht es nicht mehr nur um Kosteneinsparungen; Es wird zu einem kritischen Engpass für die Skalierbarkeit der KI.

Die Lösung von PowerLattice: Ein kleiner Chip mit großer Wirkung

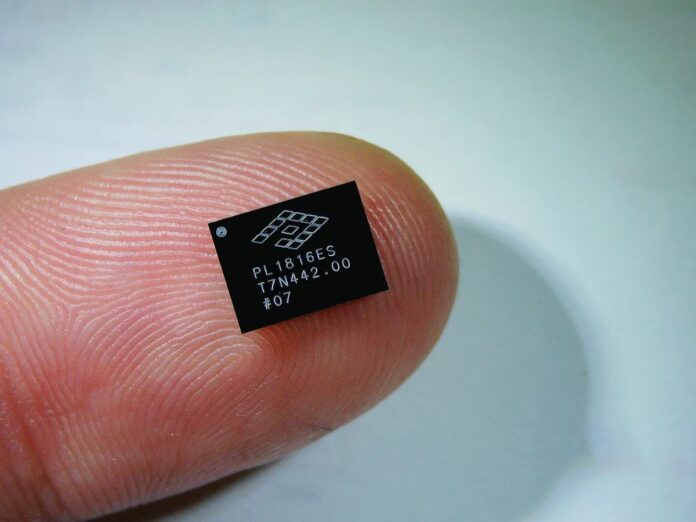

Die Kerninnovation des Startups ist ein kompakter Power-Delivery-Chiplet, der die Leistung näher an den Prozessor bringt und so den Energieverlust bei der Übertragung minimiert. Dieses scheinbar einfache Konzept adressiert eine grundlegende Herausforderung im Chipdesign: eine effiziente Stromverteilung. Die Technologie hat bereits einen wichtigen Meilenstein erreicht: Die erste Charge von Chiplets wird jetzt bei TSMC produziert, in Zusammenarbeit mit einem ungenannten Hersteller, der derzeit seine Funktionalität testet.

Branchenvalidierung: Unterstützung von Pat Gelsinger

Besonders hervorzuheben ist die Investitionsrunde durch die Beteiligung von Pat Gelsinger, ehemaliger CEO von Intel und jetzt General Partner bei Playground Global. Die Unterstützung von Gelsinger ist in der Halbleiterindustrie von großer Bedeutung und signalisiert großes Vertrauen in die Technologie von PowerLattice. Er beschrieb das Team des Startups als „das Traumteam der Energieversorgung“ und betonte dessen umfassende Fachkompetenz auf diesem Gebiet.

Tests und Erweiterung: Ausrichtung auf große Chiphersteller

PowerLattice plant, sein Produkt im ersten Halbjahr 2026 anderen Kunden zum Testen zur Verfügung zu stellen. Das Unternehmen zielt auf große Player wie Nvidia, Broadcom, AMD und spezialisierte KI-Chip-Entwickler wie Cerberus, Grok, d-Matrix und NextSilicon. Während viele Chiphersteller interne Anstrengungen zur Verbesserung der Energieeffizienz unternehmen, möchte PowerLattice eine disruptive Alternative anbieten.

Wettbewerb und zukünftige Förderung

PowerLattice wird mit anderen Start-ups im Bereich Energieeffizienz konkurrieren, insbesondere mit Empower Semiconductor, das kürzlich in einer Serie-D-Runde 140 Millionen US-Dollar eingesammelt hat. Gelsinger ist jedoch zuversichtlich, dass der Effizienzgewinn von PowerLattice um 50 % „außergewöhnlich“ ist und erhebliche Marktanteile gewinnen wird. Er geht davon aus, dass das Unternehmen bald eine größere Finanzierungsrunde abschließen wird, um die Produktion zu steigern.

The Takeaway: Eine entscheidende Lösung für die Zukunft der KI

Die Technologie von PowerLattice adressiert ein wachsendes Problem in der Halbleiterindustrie. Durch eine erhebliche Reduzierung des Stromverbrauchs könnte das Startup ein wichtiger Wegbereiter für die nächste Generation von KI-Systemen werden. Die Unterstützung des Branchenveteranen Pat Gelsinger, gepaart mit frühen Produktionsmeilensteinen, positioniert PowerLattice als ernstzunehmenden Konkurrenten im Wettlauf um die Optimierung der Energieeffizienz beim Chipdesign