Організація pci-sig на цьому тижні оголосила, що специфікації pcie 6.0 досягли статусу final draft, що є важливою віхою, що знаменує завершення розробки стандарту. Всі чіпи, сумісні зі специфікацією pcie 6.0 версії 0.9, будуть сумісні з останньою версією 1.0.

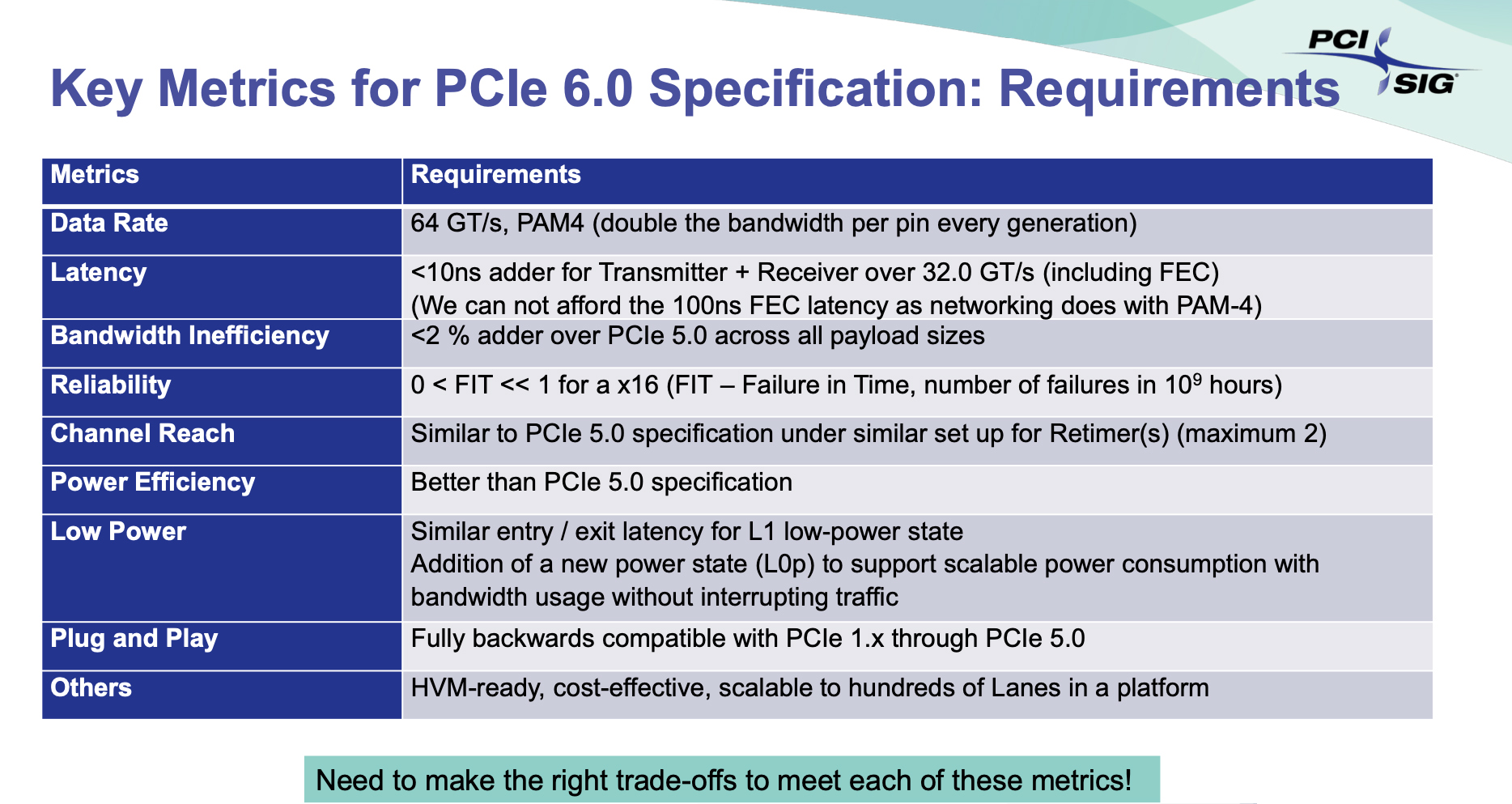

Pcie gen6 збільшить швидкість передачі даних до 64 гт/с на контакт, що в два і чотири рази більше відповідно 32 гт/с для pcie gen5 і 16 гт/с для pcie gen4. Новий стандарт збереже зворотну сумісність з існуючим нині обладнанням. Нова технологія дозволить передавати дані зі швидкістю до 128 гб в секунду в кожному напрямку по інтерфейсу x16.

Розробка специфікації pci express мають п’ять основних етапів: концепція, перший проект, повний проект, остаточний проект і фінал. Випуск специфікації pcie 6.0 complete draft (версія 0.7) трохи менше року тому дозволив великим компаніям і розробникам, таким як synopsys, почати створювати свої контролери pcie 6.0. Публікація остаточних специфікації pcie 6.0 (версія 0.9) знаменує собою точку, після якої ніякі функціональні зміни вже не допускаються.

Ті компанії, яким вдалося додати підтримку pcie 6.0 версії 0.9 в свої системи на кристалі (soc), теоретично можуть почати продавати їх як pcie 6.0 ready, але вони не зможуть офіційно підтвердити відповідність остаточної версії pcie 6.0 1.0, оскільки в даний час немає офіційної програми відповідності pcie 6.0.

Щоб зробити можливими такі швидкості передачі даних і пропускну здатність, розробники нового стандарту повинні застосовувати амплітудно-імпульсну модуляцію з чотирма рівнями (pam-4) сигналізації, яка також використовується для високопродуктивних мережевих технологій, таких як infiniband, а також пам’яті gddr6x. Крім того, pcie gen6 підтримує пряме виправлення помилок з малою затримкою (fec) для забезпечення високої ефективності при високих швидкостях передачі даних.

Хоча pcie 6.0 є важливим кроком у розвитку інтерфейсу, він також створює численні проблеми для розробників мікросхем. По-перше, pam – 4 є дорогим з точки зору потужності та розміру кристала, тому він не набув широкого поширення, крім стандартів 100gbe та 200gbe для центрів обробки даних або мережевих стандартів корпоративного рівня. По-друге, 64 гт / с є дуже високою швидкістю передачі даних, і хоча pam – 4 з fec допомагає усунути з деякі труднощі, передачу сигналу по друкованим платам (pcb) необхідно оптимізувати для зниження перехресних перешкод і втрат, відображень.

Це означає, що не всі розробники soc будуть прагнути додавати підтримку pcie 6.0 через проблеми з ціною і енергоспоживанням. Крім того, реалізація pcie 6.0 на системному рівні вимагатиме складних друкованих плат. Інтерфейс pcie 6.0 має сенс для серверів і спеціалізованих систем, але може бути занадто дорогим для масового використання на початковому етапі розгортання.